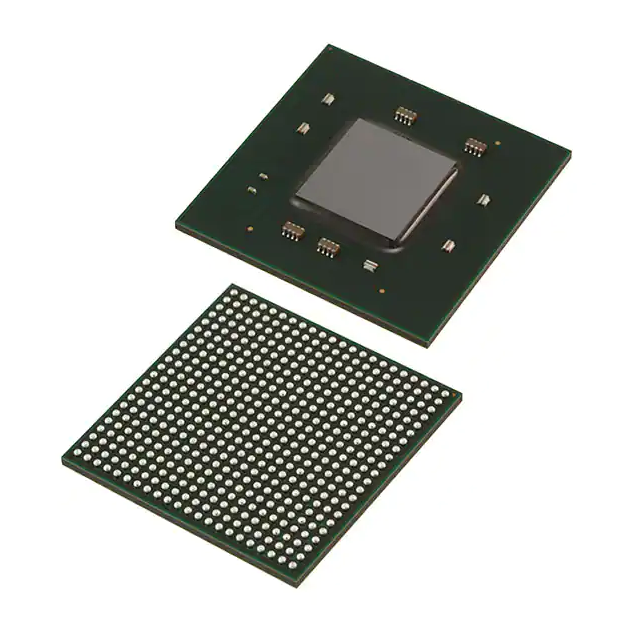

Ново и оригинално КСЦ7А100Т-2ФГГ484И ИЦ интегрисано коло ФПГА поље програмабилно поље капија ад8313 ИЦ ФПГА 285 И/О 484ФБГА

Атрибути производа

| ТИП | ОПИС |

| Категорија | интегрисана кола (ИЦ)Ембеддед |

| Произ | АМД Ксилинк |

| Сериес | Артик-7 |

| Пакет | Послужавник |

| Стандард Пацкаге | 60 |

| Статус производа | Активан |

| Број ЛАБ/ЦЛБ-ова | 7925 |

| Број логичких елемената/ћелија | 101440 |

| Укупан број РАМ битова | 4976640 |

| Број И/О | 285 |

| Напон – напајање | 0,95В ~ 1,05В |

| Тип монтаже | Сурфаце Моунт |

| Радна температура | -40°Ц ~ 100°Ц (ТЈ) |

| Пакет / Цасе | 484-ББГА |

| Пакет уређаја добављача | 484-ФБГА (23×23) |

| Основни број производа | КСЦ7А100 |

Коришћење ФПГА као процесора саобраћаја за безбедност мреже

Саобраћај до и од безбедносних уређаја (заштитних зидова) је шифрован на више нивоа, а Л2 шифровање/дешифровање (МАЦСец) се обрађује у мрежним чворовима слоја везе (Л2) (прекидачи и рутери).Обрада изван Л2 (МАЦ слоја) обично укључује дубље рашчлањивање, дешифровање Л3 тунела (ИПСец) и шифровани ССЛ саобраћај са ТЦП/УДП саобраћајем.Обрада пакета укључује рашчлањивање и класификацију долазних пакета и обраду великих обима саобраћаја (1-20М) са великом пропусношћу (25-400Гб/с).

Због великог броја потребних рачунарских ресурса (језгара), НПУ-ови се могу користити за релативно већу брзину обраде пакета, али ниско кашњење, скалабилна обрада саобраћаја високих перформанси није могућа јер се саобраћај обрађује коришћењем МИПС/РИСЦ језгара и заказивање таквих језгара на основу њихове доступности је тешко.Употреба сигурносних уређаја заснованих на ФПГА може ефикасно елиминисати ова ограничења ЦПУ и НПУ базираних архитектура.

Сигурносна обрада на нивоу апликације у ФПГА

ФПГА су идеални за инлине безбедносну обраду у заштитним зидовима следеће генерације јер успешно задовољавају потребу за већим перформансама, флексибилношћу и радом са малим кашњењем.Поред тога, ФПГА такође могу имплементирати безбедносне функције на нивоу апликације, које могу додатно уштедети рачунарске ресурсе и побољшати перформансе.

Уобичајени примери безбедносне обраде апликација у ФПГА укључују

- ТТЦП мотор за истовар

- Подударање регуларног израза

- Асиметрична енкрипција (ПКИ) обрада

- ТЛС обрада

Сигурносне технологије следеће генерације које користе ФПГА

Бројни постојећи асиметрични алгоритми су рањиви на компромитовање од стране квантних рачунара.На асиметричне безбедносне алгоритме као што су РСА-2К, РСА-4К, ЕЦЦ-256, ДХ и ЕЦЦДХ највише утичу технике квантног рачунарства.Истражују се нове имплементације асиметричних алгоритама и НИСТ стандардизације.

Тренутни предлози за пост-квантну енкрипцију укључују метод учења на основу грешке (Р-ЛВЕ) за

– Криптографија јавног кључа (ПКЦ)

- Дигитални потписи

- Креирање кључа

Предложена имплементација криптографије јавног кључа укључује одређене добро познате математичке операције (ТРНГ, Гаусов узоркивач шума, сабирање полинома, дељење квантификатора бинарног полинома, множење итд.).ФПГА ИП за многе од ових алгоритама је доступан или се може ефикасно имплементирати коришћењем ФПГА градивних блокова, као што су ДСП и АИ мотори (АИЕ) у постојећим и Ксилинк уређајима следеће генерације.

Ова бела књига описује имплементацију Л2-Л7 безбедности користећи програмабилну архитектуру која се може применити за убрзање безбедности у рубним/приступним мрежама и заштитним зидовима следеће генерације (НГФВ) у мрежама предузећа.